Product Details

Product Description

Product Description

describe

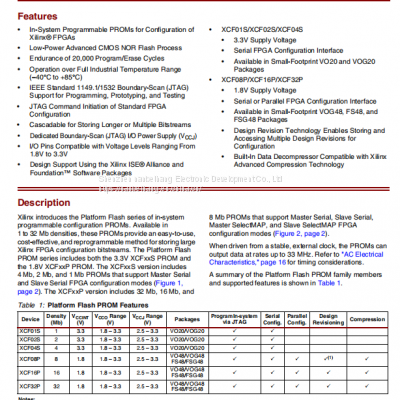

Xilinx introduces the programmable configuration prom in the system. These proms have a density of 1 to 32 MB, which is a reprogrammable method to store the configuration bit stream of large Xilinx FPGA. The platform flash Prom series includes 3.3vxcfxxsprom and 1.8vxcfxxpprom. The xcfxxs version includes 4MB, 2MB and 1MB FPGAs, which support master serial and slave serial FPGA configuration modes (Figure 1, page 2). The xcfxxp version includes 32MB, 16MB and 8MB proms, which support master serial, slave serial, master select map and slave select mapfpga configuration modes (Figure 2, page 2).

When driven from a stable external clock, prom can output data at a rate of up to 33MHz. For timing considerations, refer to "AC electrical characteristics" on page 16.

Table 1 summarizes the platform flashprom family members and supported features.

When the FPGA is in the main serial mode, it will generate a configuration clock that drives the prom. For cfhigh, if the access time is short after CE and OE are enabled, data can be obtained on the promdata (D0) pin connected to the fpgadin pin. After each rising clock edge, new data has a shorter access time. FPGA generates an appropriate number of clock pulses to complete the configuration.

When FPGA is in slave serial mode, both PROM and FPGA are clocked by external clock source, or alternatively, prom can be used to drive the configuration clock of FPGA only for xcfxxpprom.

Xcfxxp platform flashprom also supports master select map and slave select Map (or slave parallel) FPGA configuration mode. When the FPGA is in the master select map mode, the FPGA will generate a configuration clock that drives the prom. When the FPGA is in the dependent selection map mode, or an external oscillator generates the configuration clock driving the prom and FPGA, or you can choose to use xcfxxpprom to drive the configuration clock of the FPGA. Using busylow and cfhigh, data can be obtained on the Proms data (d0-d7) pin after CE and OE are enabled. After each rising clock edge, new data has a shorter access time. Data is recorded to the FPGA at the rising edge of CCLK. A free running oscillator can be used in slave parallel / slave select map mode.

The xcfxxp version of the platform flash Prom provides additional advanced functionality. The built-in data decompressor supports the use of compressed Prom files, and design modifications allow multiple design revisions to be stored on a single prom or in multiple proms. For design revisions, use external pins or internal control bits to select the active design revision.

When targeting larger FPGA devices or multiple FPGAs, multiple platform flashprom devices can be cascaded to support the required larger configuration files. When using the advanced functions of flash Prom of xcfxxp platform, such as design revision, you can only create programming files for the cascading chain of cross cascaded Prom devices that only contain xcfxxpprom. If the advanced xcfxxp feature is not enabled, the cascade chain can include both xcfxxp and xcfxxsproms.

features

• programmable proms in the system for configuration

Xilinx ® FPGA

• low power advanced CMOS NOR Flash Technology

• durability of 20000 program / erase cycles

• operate over the entire industrial temperature range

(- 40 ° C to + 85 ° C)

• IEEE standard 1149.1/1532 boundary scan (JTAG)

Support programming, prototyping and testing

• JTAG command startup of standard FPGA

to configure

• longer or more bitstreams can be stored in cascade

• dedicated boundary scan (JTAG) input / output power supply (vccj)

• I / O pins are compatible with the following voltage levels:

1.8V to 3.3V

• use Xilinx ISE ® Alliance and

foundation ™ software package

•XCF01S/XCF02S/XCF04S

• 3.3V supply voltage

• serial FPGA configuration interface

• small size vo20 and vog20

packing

•XCF08P/XCF16P/XCF32P

• 1.8V supply voltage

• serial or parallel FPGA configuration interface

• small size vog48, fs48 and

Fsg48 software package

• design revision technical support and storage

Access multiple design revisions

to configure

• Xilinx compatible built-in data decompressor

Advanced compression technology

>>

Factory Direct Sales Can Customize Lyocell Linen Fabric 32% Linen Fabric 68% Lyocell Abaya Fabric for Clothing

>>

Advanced L Profile Angle Bar Cold Forming Machine with Cr12 Roller Material

>>

Automobile Parts Perforated Metal Mesh Speaker Grill Cover

>>

Amazon hot selling Personal Traveling Home Negative Ion True HEPA Filter Portable Cleaner Car Air purifier

>>

Lace Bodysuit Wirefree Lingerie Unpadded Body Shaper

>>

Ladder Making Machines Automatic CNC Ladder Drilling Machine

>>

Car engine coolant thermostat auto parts for TOYOTA OEM 9091603122 90048-33088 90048-33088-000 16340-97401 9091603122

>>

Electric / gas type Double / single door dirty sheep wool washing machine / machine to wool washer

>>

Best Seller Stainless Steel Modern Luxury Roasting Charcoal Grill Wooden BBQ Skewers

>>

New 1:1 high-grade stainless steel diamond mechanical watch waterproof luxury commercial multi-function 42mm automatic watch

>>

Frozen Acai Brazil Berry Ice Cream Maker Commercial Soft Ice Cream Machine

>>

Automatic expansion of diamond mesh rolling machine

>>

CNC Three-Dimensional Drilling Machine for H-Beams and Channel

>>

API Spiral Pipe Mill Back-Swing SSAW Pipe Making Machine

>>

Customized Corrosion Resistance Ptef Molded Pipe Extrusion Teflonning Ptef Extruded Tube for Chemical Industry

>>

Best Seller Bendable Portable Premium Plastic Black Colour Expendable Garden Hose

>>

Low Price High Quality Aloe Vera Drink with Aloe Vera Pulp

>>

artemia cysts,brine shrimp eggs

>>

WEIKA Modern Design Hurricane Impact Double Tinted Glass Aluminum Frame Sliding Window Customized

>>

Earth-Moving Machinery Xe215da 21.5 Ton 21 Ton Mini Digger Excavator 20 Ton 21ton New Hydraulic Crawler Excavator for Sale